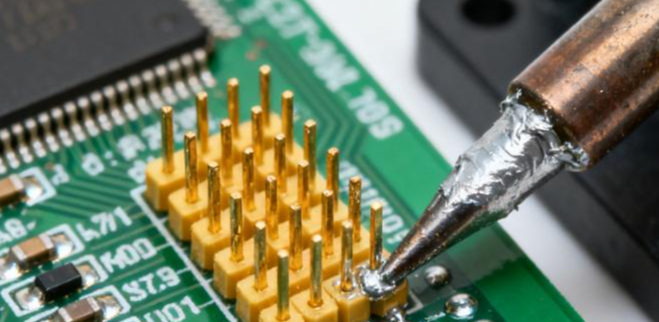

PCBパッドのはんだ付け不良解析:欠陥箇所から根本原因の亀裂まで

2026-04-03 16:20PCBA製造において、パッドのはんだ付け不良ははんだ付け不良の主な原因であり、一般的に以下のような症状が現れます。 非濡れ性、半濡れ性、錫収縮、錫浸透不良、ピンホール気泡、仮想はんだ付け、コールドはんだ付け故障解析は、単に材料を交換することではなく、欠陥の根本原因を正確に特定し、再発を防ぐための標準化されたプロセスです。

ステップ1:現場での欠陥収集と予備判定

濡れない: はんだが全く広がっておらず、パッドの金属が露出しており、接着がない → パッドがひどく酸化され、有機物で汚染され、メッキが完全に失敗している可能性が高い。

半湿潤性: はんだが最初に広がり、その後収縮し、部分的に露出する → コーティングの局所的な欠陥、軽度の酸化、およびフラックス活性の不足。

収縮: はんだが球状に収縮し、ドットのみが付着します → 表面エネルギーが極めて低く、重度の汚染があり、OSP フィルムが完全に破壊されます。

錫の浸透性が悪い: スルーホールの穴壁が濡れていない → 穴壁の汚染、コーティングの漏れ、予熱不足、ディップはんだ付け時間が短すぎる。

ピンホール気泡: はんだ層の空洞 → 基板が水分、フラックス水蒸気、パッド酸化膜を吸収する。

黒いディスクには非濡れ性が伴いますENIGパッドが黒くなっている → 典型的なニッケル層の腐食による故障。

ステップ2:標準化されたはんだ付け性再テスト検証

ステップ3:実験機器の詳細なテスト

- 金属組織顕微鏡/走査型電子顕微鏡 パッドの微細構造を観察します。酸化層の厚さ、めっきピンホール、剥離、黒ニッケル、ウィスカー、有機残留物、およびIMC層の形態などを確認します。SEMは数千倍まで拡大できるため、ENIGブラックディスクのニッケル層の腐食穴やOSP膜の亀裂など、ナノスケールの欠陥を明確に識別できます。

- EDSエネルギー分光法 パッド表面の元素組成を検出します。O(酸素)含有量が高い場合は、深刻な酸化を示しています。C(炭素)含有量が高い場合は、有機汚染を示しています。S(硫黄)/Cl(塩素)含有量が高い場合は、硫化物/塩化物イオンの腐食を示しています。ENIGパッドはAu含有量が低すぎ、Ni含有量が異常であるため、めっきが効果的でないことを示しています。

- XRFコーティング厚さ計 非破壊によるめっき膜厚測定:OSP膜厚は0.2~0.5μmが合格、ENIGニッケル層は3~5μm、金層は0.05~0.15μmが合格、浸漬錫/銀層の厚さは規格を満たしている。膜厚が不十分または著しく不均一な場合は、溶接性不良に直接つながる。

- 表面清浄度試験(イオン汚染試験) パッド表面のイオン残留物(塩化物イオン、ナトリウムイオン、カリウムイオンなど)を検出します。これらのイオン残留物は基準値を超えており、濡れ界面を損傷し、腐食やはんだ付け不良の原因となります。業界標準では、イオン汚染は1.56 μg/cm²(NaCl換算)未満であることが求められています。

- 湿潤バランス試験機 濡れ力-時間曲線の定量的分析:良品サンプルと比較すると、不良サンプルは通常、負の濡れ力、濡れ時間が長すぎる、F5の90%を示します。

ステップ4:故障メカニズムの解明と根本原因の特定

典型的な故障事例1:OSPボードが広い範囲を濡らさない

典型的な故障事例2:ENIGパッドが部分的に濡れている+黒いディスク

典型的な失敗事例3:浸漬銀板の加硫処理が溶接不良を引き起こす

典型的な失敗事例4:錫溶射プレートの浸透不良

典型的な失敗事例5:バッチ式錫還元

ステップ5:プロセス検証と改善計画の実施

コーティング欠陥の改善OSPコーティングパラメータを調整して均一な膜厚を確保する。ENIGニッケルゴールドプロセスを最適化して黒ディスクをなくす。電気めっき制御を強化して漏れや剥離を防ぐ。

汚染対策の改善イオン残留物を減らすために洗浄プロセスをアップグレードする。帯電防止および無塵作業を行い、パッドに素手で触れない。インクの溢れを防ぐためにソルダーマスクプロセスを最適化します。

保管および輸送の改善: 厳密な真空包装、乾燥剤と湿度カードの増加。FIFO管理と保管サイクルの制御の実施。硫化物/塩化物イオン汚染を避けるために保管温度と湿度を改善。

プロセスマッチングの改善: 表面処理の種類に合わせて溶接温度/時間/予熱を最適化する。活性と適合性を向上させるために適切なフラックスを選択する。

制御とアップグレード工場における溶接性抜き取り検査の割合を増やし、主要製品の経年劣化試験を強化する。入荷材料の再検査システムを確立し、期限切れ鋼板の強制検査を実施する。